Texas Instruments CDCDB803 8-Output Clock Buffer for PCIe® Gen 1 - 5

Texas Instruments CDCDB803 8-Output Clock Buffer for PCIe® Gen 1 to Gen 5 is a DB800ZL compliant clock buffer that distributes the reference clock for PCIe Gen 1-5, QuickPath Interconnect (QPI), UPI, SAS, and SATA interfaces. The SMBus interface and eight output enable pins permit the configuration and control of all eight outputs individually.The TI CDCDB803 is a DB800ZL derivative buffer and meets or exceeds the system parameters in the DB800ZL specification. Additionally, the buffer meets or exceeds the parameters in the DB2000Q specification.

The CDCDB803 Clock Buffer is housed in a 6mm × 6mm, 48-pin VQFN package.

Features

- 8 LP-HCSL outputs with programmable integrated 85Ω (default) or 100Ω differential output terminations

- 8 hardware output-enable (OE#) controls

- Additive phase jitter after PCIE Gen5 filter of <25fs, RMS (maximum)

- Additive phase jitter after DB2000Q filter of <38fs, RMS (maximum)

- Supports PCIe Gen 4 and Gen 5 Common Clock (CC) and Individual Reference (IR) architectures

- Spread spectrum-compatible

- <50ps Output-to-output skew

- <3ns Input-to-output delay

- Fail-safe input

- Programmable output slew rate control

- 9 selectable SMBus addresses

- 3.3V core and IO supply voltages

- Hardware-controlled low power mode (PD#)

- Current consumption of 72mA maximum

- 6mm × 6mm, 48-pin VQFN package

Applications

- Microserver and tower server

- Storage area network and host bus adapter card

- Network-attached storage

- Hardware accelerator

- Rack server

Additional Resources

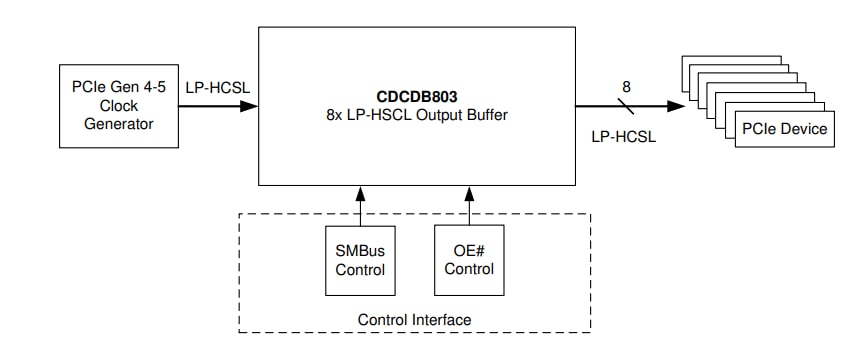

System Diagram

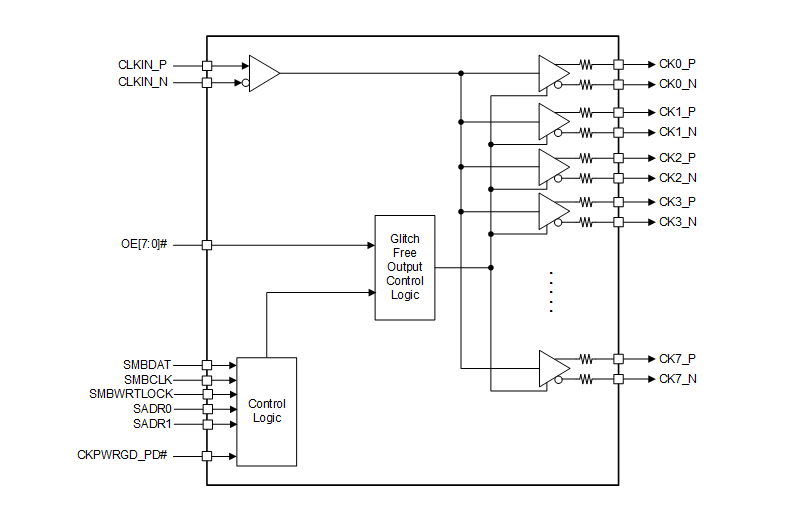

Functional Block Diagram

Published: 2021-10-08

| Updated: 2023-12-18